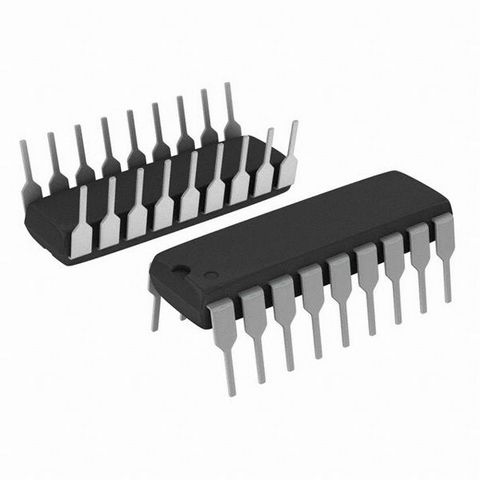

DM74S572NFIFO 4K (1K x 4) 60ns 18-PDIP

N/A

Orders Over $2000 Receive a $100 Discount for Registered Abrmicro Users.

ABRmicro #.ABR2019-DM74S5-1887460

ManufacturerOnsemi

MPN #.DM74S572N

Estimated Lead Time-

SampleGet Free Sample

For large-volume purchases, our unique channels enable us to provide prices that other suppliers cannot match: significantly below market rates.

Service

Guaranteed Authenticity

Guaranteed Authenticity Technical Support

Technical Support Fast Refund

Fast Refund Free Shipping (over $960)

Free Shipping (over $960) Issue an Invoice

Issue an Invoice 24/7 Manual Service

24/7 Manual Service In Stock: 19

Shipped From Shenzhen or Hong Kong Warehouses

Min.&Mult.1

Packaging

Bag

Shipping DateNovember 3, 2024

* Quantity

Send Inquiry

Add To RFQ List

Related Parts

NLV74HC174ADR2G$0.4420

Flip Flop 1 Element D-Type 6 Bit Positive Edge 16-SOIC (0.154", 3.90mm Width) Technical Specifications

Series74S

Packaging

Bag

Lifecycle StatusObsolete

Access Time60ns

Base Product Number74S572

Bus Directional-

Supply Current (Max.)-

Data Rate-

Expansion Type-

FWFT SupportNo

Function-

Memory Size4K (1K x 4)

Mounting StyleThrough Hole

Operating Temperature0°C ~ 70°C

Parameter ProgrammingSupported

Programmable Flags SupportNo

Retransmit CapabilityNo

Package Type (Mfr.)18-PDIP

Supply Voltage4.75 V ~ 5.25 V

Package / Case18-DIP (0.300", 7.62mm)

Customize Part Specifications , or Contact Our Sales Representative to Obtain the Data You Desire info@Abrmicro.com

info@Abrmicro.com

info@Abrmicro.com

info@Abrmicro.comExtended Links

Environmental Information

Environmental & Export Classifications

RoHS ComplianceNot RoHS compliant and cannot enter the EU market

MSL Level1 (Unlimited, ≤ 30°C/85% RH), No special packaging

REACH RegulationNo SVHCs Present

US ECCNEAR99

HTSUS8542.39.0001 (No rates found in the Harmonized Tariff Schedule)